AMD وصلهای ارائه میکند که تاخیر بین هستهای و تراشههای Ryzen 9000 Zen 5 را بهبود میبخشد

طبق گزارشها، AMD در حال کار بر روی یک وصله جدید بایوس است که به بهبود تاخیر بین هستهای در پردازندههای دسکتاپ Ryzen 9000 “Zen 5” کمک میکند.

CPU های Ryzen 9000 “Zen 5” AMD برای مشاهده پیشرفت های بیشتر در حالی که تیم Red قصد دارد پچ بایوس را برای بهبود تاخیرهای بین هسته ای عرضه کند

پردازندههای دسکتاپ Ryzen 9000 مبتنی بر Zen 5 AMD عملکردی را که همه انتظارش را داشتیم افزایش ندادند. اگرچه یکی از دلایل این امر را می توان بهینه سازی ضعیف ویندوز 11 نسبت داد، اما این تنها دلیل نیست. Core Parking بهینهنشده یکی از عواملی است که ظاهراً به دلیل نرمافزار ناتمام و پشتیبانی بایوس، عملکردی کندتر از ایدهآل دارد.

Geekerwan: AMD مشکل تأخیر Zen 5 C2C را برطرف خواهد کرد.https://t.co/v1ru4UXQmS< /a> pic.twitter.com/3u0pAmBuwV

— HXL (@9550pro) 27 اوت 2024

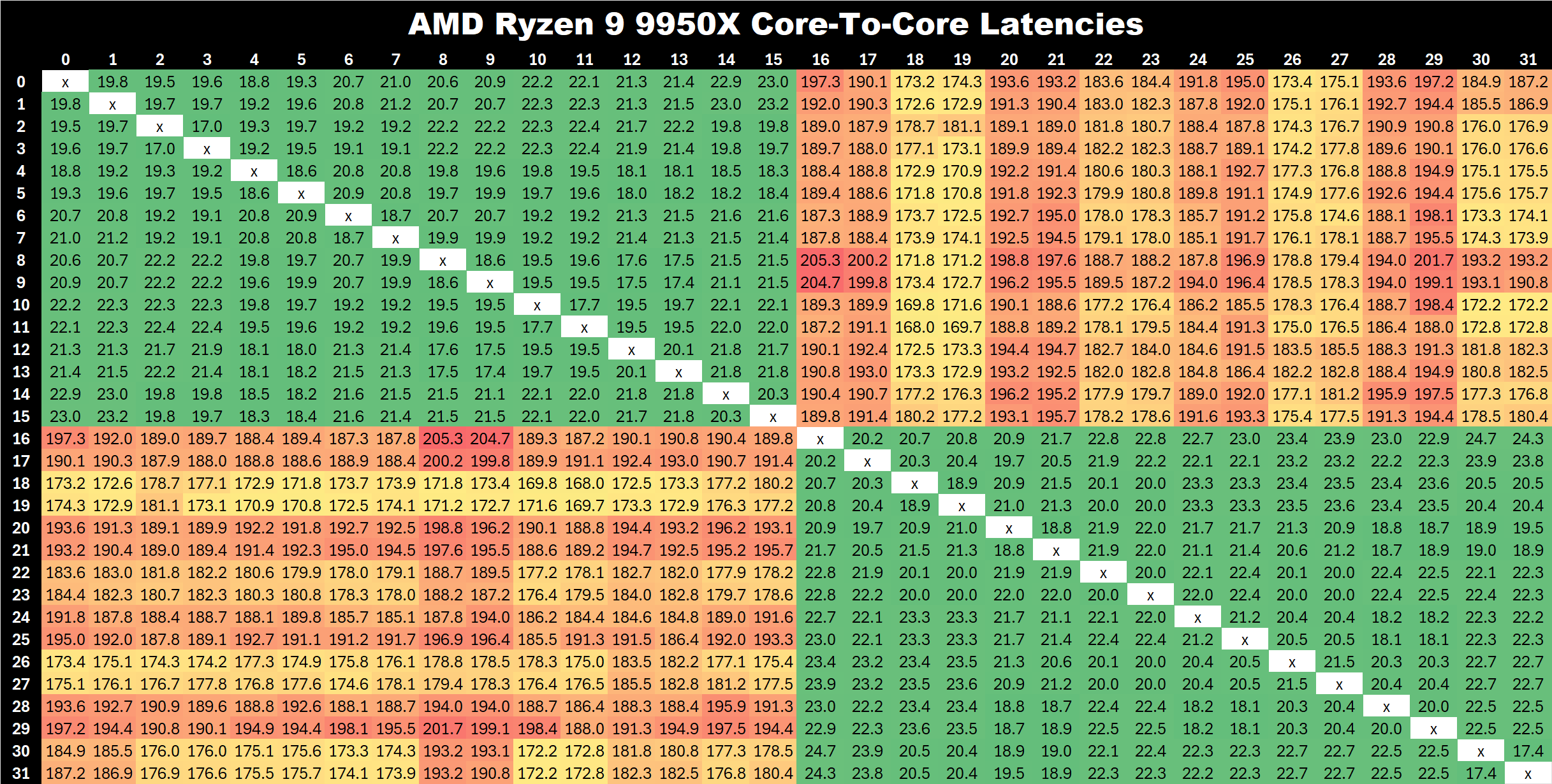

در Anandtech با بررسی Ryzen 9 9950X، مشخص شد که CPU Zen 5 در مقایسه با نسل قبلی خود تأخیر بین CCD به طور قابل توجهی بالاتر است. این در حالی است که هر دو CPU Zen 4 و Zen 5 طراحی مشابهی با قالب I/O و پارچه بی نهایت دارند. با این حال، گزارش اخیر Geekerwan در Bilibili (از طریق @9950pro) نشان می دهد که AMD در حال کار برای رفع این مشکل از طریق یک پچ BIOS آینده است.

تأخیر بین CCD به سرعت انتقال داده ها یا دستورالعمل ها بین دو CCD Zen 5 (مرگ های مجتمع هسته) در پردازنده های Ryzen 9000 است. این پارچه برای ارتباط با چیپلت های متعدد مانند CCD و IOD استفاده می شود. از آنجایی که Ryzen 9 9950X و Ryzen 9 9900X حاوی دو CCD هستند که هر CCD دارای 8 هسته Zen 5 است، برنامه هایی که از بیش از 8 هسته استفاده می کنند باید داده ها را بین CCD ها برای اجرای سریعتر منتقل کنند.

متأسفانه، برخلاف مدل قبلی خود Ryzen 9 7950X، AMD Ryzen 9 9950X تقریباً دو برابر تاخیر CCD به CCD در مقایسه با قبلی است. میانگین تأخیر بین CCD برای Zen 5 به طور متوسط 180 ثانیه در مقایسه با 76 ثانیه در 7950X است. این منجر به انتقال دادههای کندتر بین CCDها میشود، و در نتیجه عملکرد چند رشتهای کندتر از حد انتظار در برخی از بارهای کاری انجام میشود.

تأخیر بالاتر بین CCD به دلیل طراحی قالب نیست، بلکه به دلیل بهینهسازیهای ناتمام و صیقلنشده AMD در پشته نرمافزار BIOS و چیپست است. همانطور که در گزارش جدید پیشنهاد شده است، AMD تاخیر بالای بین CCD را از طریق بهروزرسانی بایوس که در ماههای آینده عرضه میشود، برطرف خواهد کرد.

امیدواریم که با آپدیت جدید شاهد افزایش عملکرد خواهیم بود اما تاریخ دقیق به روز رسانی بایوس هنوز مشخص نیست. با این حال، این اصلاح لزوماً بر عملکرد بازی تأثیر نمی گذارد زیرا بیشتر بازی ها از بیش از یک CCD حاوی 8 هسته استفاده نمی کنند. در برنامه هایی که می توانند از بیش از 8 هسته استفاده کنند، رفع تأخیر بین CCD می تواند برخی از مشکلات عملکرد را حل کند.

همین دیروز، AMD اعلام کرد که بهینهسازیهای پیشبینی شعب در Windows 11 23H2 از طریق Backporting، که منجر به افزایش عملکرد همانطور که در Windows 11 24H2 دیده میشود. بنابراین، بدیهی است که AMD احتمالاً در راهاندازی سری ناتمام Ryzen 9000 عجله کرده است، که به بهینهسازیهای بیشتری برای ارائه برخی ارتقاء نسلی قابل توجه نیاز دارد.

منبع خبر: بررسی نوت بوک